https://doi.org/10.33180/InfMIDEM2019.104

# Design and Performance Analysis of Hybrid SELBOX Junctionless FinFET

Rajeev Pankaj Nelapati, Sivasankaran K.

School of Electronics Engineering, Vellore Institute of Technology, Vellore, India

**Abstract:** In this work, the performance of selective buried oxide junction-less (SELBOX-JL) transistor at a FinFET structure is analysed using numerical simulations. The proposed structure exhibits better thermal resistance ( $R_{TH}$ ), which is the measure of the self-heating effect (SHE). The DC and analog performances of the proposed structure were studied and compared with the conventional and hybrid (or inverted-T) JLFinFETs (JLTs). The  $I_{ON}$  of the hybrid SELBOX- JLFinFET is 1.43x times better than the ION of the JLT due to the added advantage of different technologies, such as 2D-ultra-thin-body (UTB), 3D-FinFET, and SELBOX. The proposed device is modeled using sprocess and simulation study is carried using sdevice. Various analog parameters, such as transconductance ( $g_m$ ), transconductance generation factor (TGF =  $g_m$ / $I_{DS}$ ), unity current gain frequency ( $f_T$ ), early voltage ( $V_{EA}$ ), total gate capacitance ( $C_{gg}$ ), and intrinsic gain ( $A_0$ ), are evaluated. The proposed device with a minimum feature size of 10nm exhibited better TGF,  $f_{Tr}$   $V_{EA}$ , and  $A_0$  in the deep-inversion region of operation.

**Keywords:** Junctionless FinFET, Hybrid SELBOX-JLFinFET, Self heating, f<sub>T</sub>, TGF.

# Analiza zasnove in učinkovitosti hibridnega brezspojnega SELBOX FinFET-a

**Izvleček:** V članku je analiziran brezspojni SELBOX-JL transistor v FinFET strukturi. Predlagana struktura izkazuje boljšo termično upornost, ki je merjena preko lastnega segrevanja. DC in analogne lastnosti predlagan strukture so primerjanes konvencionalnimi in hibridnimi strukturami. Tok hibridnega SELBOX-JLFinFET je 1.43-krat boljši kot pri JLT zaradi uporabe drugačne tehnologije, kot je 2D ultra tanko ohišje, 3D-FinFET in SELBOX. Ocenjeni so številni parametri, kot je transkonduktanca, generacijski faktor transkonduktance, frekvenca tokovnega ojačenja, zgodnja napetost, skupna kapacitivnost vrat in osnovno ojačenje.

**Ključne besede:** Brezspojni FinFET, hibridni SELBOX-JLFinFET, lastno segrevanje,  $f_{\tau}$ , TGF.

#### 1 Introduction

Silicon on insulator (SOI) MOSFETs has numerous advantages over bulk MOSFETs such as low parasitics, better isolation, radiation hardness, improved speed, ability to operate at low V<sub>DD</sub> and higher environmental temperatures [1, 2]. The improved gate control over the channel causes FinFETs to demonstrate reduced short channel effects (SCEs), such as drain-induced barrier lowering (DIBL), when compared to MOSFETs [3,4]. However, the performance of the conventional FinFETs is overshadowed by hybrid FinFETs by effective utilization of the device area. A higher drain current is attained in hybrid FinFET by employing the unused area in conventional FinFET. The added advantages of the SOI and ultra-thin body (UTB) technologies enable the hybrid FinFET to have more drain current for the same

fin width ( $W_{\rm fin}$ ) and gate length ( $L_{\rm g}$ ) when compared to conventional FinFETs. Zhang et al. proposed hybrid FinFET [5] and was later explored by Fahad et al. in [6]. Subsequently, the impact of high-k symmetric and asymmetric spacer, fin shape, and temperature on the performance of the hybrid FinFETs were analyzed by Pradhan et al. [7,8,9,10]; and the effect of self-heating on the performance of hybrid FinFETs was studied by Nelapati et al.[11].

Continuous scaling of electronic devices led to the difficulty of having sharp doping profiles in inversion mode (IM) transistors. Consequently, this led to the invention of the transistor without junctions. Colinge et al. [12] demonstrated a junctionless transistor (JLT), which is free from the junction and any doping gradients. A

<sup>\*</sup> Corresponding Author's e-mail: rajeevpankaj@vit.ac.in

comparative study of SOI-JLT and bulk JLT was carried in [13]. SOI-JLT is better than the bulk JLT but lacks in thermal conductivity due to the presence of silicon dioxide as a buried oxide. Self-heating in SOI devices can be reduced by replacing silicon dioxide with better thermally conductive materials or by modifying the device structure [14, 15]. Narayanan *et al.* proposed a modified SOI device structure for reducing the self-heating effect [16]. In this structure, the buried oxide is patterned in the selective region under the source and drain, and not continuously, which is referred to as the SELBOX struc-

(a) Gate Source Drain Oxide BOX Substrate (b) Drain Source Oxide BOX Substrate (c) Drain Gate Source Oxide Substrate

Figure 1: (a) Coventional JLT (SOI-JLT) (b) HJLT (c) HSJLT.

ture. Uzma *et al.* presented a comparative study of planar SELBOX and SOI junctionless transistors [17].

In this work, we analyzed the performance of hybrid SELBOX-JLFinFET (HSJLT), which is immune to self-heating and delivers higher drain current. The proposed structure adds the advantage of UTB, SOI technology, and SELBOX structure. Figure 1 depicts the 3-D view of conventional JLT, hybrid JLFinFET (HJLT), and HSJLT. The DC and analog performance of HSJLT are evaluated and compared with conventional and hybrid JLTs. The rest of the paper is organized as follows: Section 2 discusses the process flow of the proposed device and the simulation setup. Section 3 discusses the DC characteristics, self-heating effect, and analog performance of HSJLT and the comparison of simulation results with conventional and hybrid JLTs. The conclusions are drawn in Section 4.

### 2 Process flow and Simulation Setup

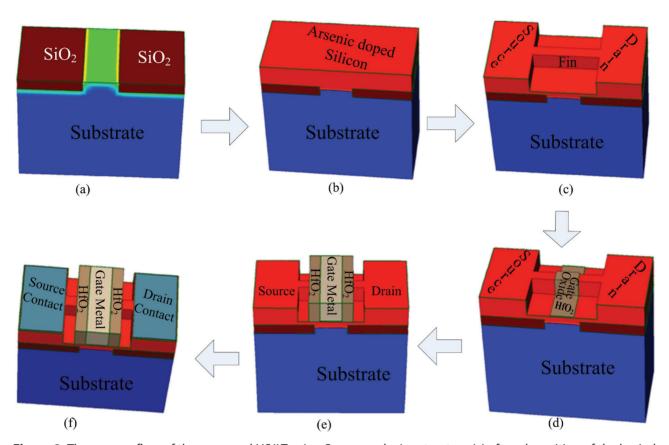

Figure 2 shows the process flow adopted for modeling the proposed HSJLT using sentaurus process (sprocess) [18]. Silicon material is defined as a substrate with underlying doping of boron (5x10<sup>18</sup> cm<sup>-3</sup>). The insulating material, SiO<sub>2</sub>, is deposited as a buried oxide on the selective regions by masking. The device structure after the BOX patterning is shown in Figure 2(a). The silicon material for the fin is deposited as shown in Figure. 2(b) with uniform doping of arsenic (1x10<sup>19</sup> cm<sup>-3</sup>) and by masking, followed by etching the fin of the transistor is defined as shown in Figure. 2(c). HfO<sub>2</sub> is deposited as shown in Figure 2(d), which serves as the gate dielectric. Figure 2(e) shows the device structure after the deposition of the gate metal and spacer material. Finally, the metallization is carried for the contact of the source and drain, as shown in Figure 2(f).

Table 1 shows the device specifications and doping profiles of the three devices considered for the simulation. The OFF current ( $I_{OFF}$ ), of the three devices shown in Figure 1, is adjusted to  $\approx$  1pA by tuning the gate metal work function (GWF). The GWF for conventional JLT, HJLT, and HSJLT is 4.72eV, 4.87eV, and 4.7eV, respectively. The GWF of HJLT is larger because the ultra-thin body transistor in hybrid devices will be turning on early when compared to fin transistor [6]. The GWF of HSJLT is smaller when compared to HJLT because the planar transistor's gate is depleted in HSJLT by both GWF and the depletion region formed by the oppositely doped substrate [19].

The sentaurus device (sdevice) is used to conduct device simulations [20]. Mobility degradation models,

**Figure 2:** The process flow of the proposed HSJLT using Sprocess, device structure (a) after deposition of the buried oxide (b) after epitaxial growth of silicon for fin (c) after definition of the fin (d) after gate oxide (HfO<sub>2</sub>) deposition (e) after gate metal and spacer deposition (f) after contact definition

such as transverse field (to account for degradation at interfaces), high field saturation (to account for velocity saturation effect), and doping dependence (to account for impurity scattering effect), are considered along with default carrier transport model for the device simulation. Shockley – Reed – Hall (SRH) recombination and Auger recombination models are included to account for the recombination of electrons and holes. Old-slotboom band-gap narrowing model is in-

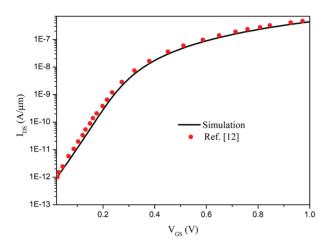

corporated due to the high doping of the channel. The self-heating effect is accounted for by the inclusion of Auger recombination models, SRH (temperature dependent), and the thermodynamic model for carrier transport. The simulator is verified by the excellent fitting of transfer characteristics of SOI junctionless transistor with the experimental data presented in [12]. Figure. 3 shows the calibration of simulation results with experimental data.

**Table 1:** Device parameters and doping profiles.

| Parameter                            | JLT                                   | HJLT                                  | HSJLT                                 |

|--------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| Gate length (L <sub>g</sub> )        | 20nm                                  | 20nm                                  | 20nm                                  |

| Fin height (H <sub>fin</sub> )       | 20nm                                  | Hfin-UTB = 16nm                       | Hfin–UTB = 16nm                       |

| Fin width (W <sub>fin</sub> )        | 10nm                                  | 10nm                                  | 10nm                                  |

| Effect oxide thickness (EOT)         | 0.9nm (HfO <sub>2</sub> )             | 0.9nm (HfO <sub>2</sub> )             | 0.9nm (HfO <sub>2</sub> )             |

| Ultra-thin body (UTB) thickness      | -                                     | 4nm                                   | 4nm                                   |

| Spacer length                        | 10nm (HfO <sub>2</sub> )              | 10nm (HfO <sub>2</sub> )              | 10nm (HfO <sub>2</sub> )              |

| Selbox length (L <sub>SELBOX</sub> ) | -                                     | -                                     | 10nm to 40nm                          |

| BOX thickness                        | 10nm                                  | 10nm                                  | 10nm                                  |

| Fin dopants (Arsenic)                | 1 X 10 <sup>19</sup> cm <sup>-3</sup> | 1 X 10 <sup>19</sup> cm <sup>-3</sup> | 1 X 10 <sup>19</sup> cm <sup>-3</sup> |

| Substrate dopants (Boron)            | 1 X 10 <sup>15</sup> cm <sup>-3</sup> | 1 X 10 <sup>15</sup> cm <sup>-3</sup> | 5 X 10 <sup>18</sup> cm <sup>-3</sup> |

| Gate metal workfunction (GWF)        | 4.72eV                                | 4.87eV                                | 4.7eV                                 |

**Figure 3:** Calibration of  $I_{DS} - V_{GS}$  characteristics of the SOI junctionless transistor with the experimental data [12] at  $V_{DS} = 1V$  and  $L_{a} = 1\mu m$ .

#### 3 Results and Discussions

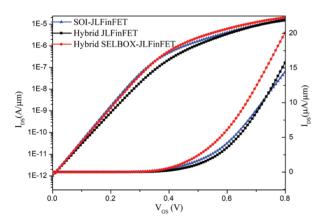

Figure 4 shows a comparison of the transfer characteristics of the three device structures calibrated to the same  $I_{OFF}$ . Figure 4 shows that the HJLT and the HSJLT deliver maximum drain current due to the added advantage of UTB and fin structures. HSJLT delivers more drain current than HJLT because of the lower threshold voltage ( $V_{TH}$ ) and low GWF.

**Figure 4:** Comparison of transfer characteristics of SOI-JLFinFET, hybrid JLFinFET, and hybrid SELBOX-JLFinFET at  $L_{\text{SELBOX}} = 20$ nm,  $V_{\text{DS}} = 0.8$ V and calibrated to same  $I_{\text{OFF}} = 1$ pA.

#### 3.1 DC performance of HSJLT

In this section, the DC performance of the HSJLT is studied for different SELBOX lengths ( $L_{\rm SELBOX}$ ) at the same  $V_{\rm TH}$ . The variations of ON current ( $I_{\rm ON}$ ),  $I_{\rm OFF}$  sub-threshold slope (SS), DIBL, lattice temperature, and  $R_{\rm TH}$  in HSJLT are presented for different  $L_{\rm SELBOX}$  and compared with the conventional and hybrid JLTs.

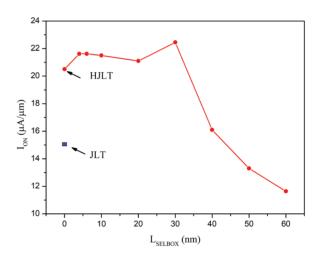

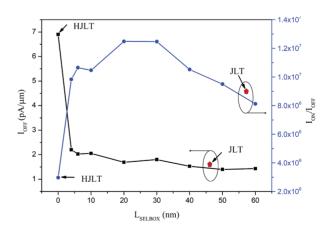

Figure 5 shows the variation of  $I_{ON}$  with the increase in  $L_{SELBOX}$ .  $L_{SELBOX}$  is the gap between the edges of the BOX material shown in Figure 1(c). As  $L_{SELBOX}$  increases, the  $I_{ON}$  of the HSJLT decreases due to the penetration of the depletion region into the active area. HJLT is a particular case of HSJLT, in which the  $L_{SELBOX}$  is zero. In hybrid transistors, the conduction of current is due to UTB transistor and fin transistor, and the UTB transistor turns on earlier than the fin transistor [6]. For the same threshold voltage, the GWF required for HSJLT is lower than the HJLT due to the depletion region provided by the SELBOX structure. Comparatively low GWF of HSJLT makes its fin transistor to turn early when compared to the fin transistor of HJLT, due to which the  $I_{ON}$  is less in HJLT when compared to HSJLT for  $L_{SELBOX}$  being < 40nm.

**Figure 5:** Variation of  $I_{ON}$  for different  $L_{SELBOX}$  of HSJLT at  $L_{q} = 20$ nm,  $V_{DS} = 0.8$ V, and  $V_{GS} = 0.8$ V.

Figure 6 shows the variation of  $I_{OFF}$  and  $I_{ON}/I_{OFF}$  for different  $L_{SELBOX}$ .  $I_{OFF}$  decreases as  $L_{SELBOX}$  increases due to the tight control of the GWF at the top and the depletion region at the bottom of the planar transistor [17].

**Figure 6:** Variation of  $I_{OFF}$  and  $I_{ON}/I_{OFF}$  for different  $L_{SELBOX}$  of HSJLT at  $L_{a} = 20$ nm,  $V_{DS} = 0.8$ V.

Initially for  $L_{SELBOX}$  < 30nm,  $I_{ON}/I_{OFF}$  ratio increases with an increase in  $L_{SELBOX}$  and this ratio decreases for  $L_{SELBOX}$  > 30nm because  $I_{ON}$  drops significantly compared to  $I_{OFF}$ .

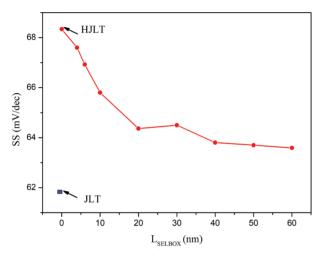

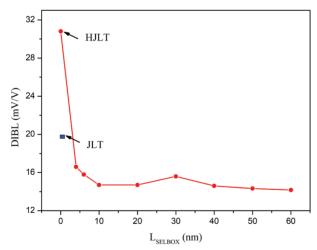

Figure 7 and Figure 8 show the variation of the SS and DIBL for different  $L_{\text{SELBOX}}$  of HSJLT. SS and DIBL decrease as the  $L_{\text{SELBOX}}$  increases due to the increase in gate control over the active region caused by an effective increase in the depletion region provided by the SELBOX at the bottom of the UTB transistor. SS and DIBL in HJLT are high because of non-uniform  $V_{\text{Tu}}$  [6].

**Figure 7:** Variation of SS for different  $L_{SELBOX}$  of HSJLT at  $L_{q} = 20$ nm,  $V_{DS} = 50$ mV.

**Figure 8:** Variation of DIBL for different  $L_{SELBOX}$  of HSJLT at  $L_q = 20$ nm,  $V_{DS,linear} = 50$ mV,  $V_{DS,saturation} = 0.8$ V.

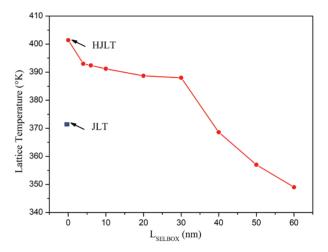

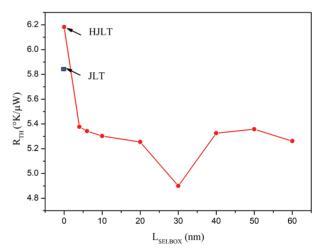

Figure 9 and Figure 10 depict the variation of thermal resistance (R<sub>TH</sub>) and lattice temperature for different L<sub>SELBOX</sub>. Thermal resistance can be used to measure the immunity to self-heating of the device; more RTH, less immunity to self-heating. R<sub>TH</sub> depends on the power dissipated (P<sub>dissipated</sub> = V<sub>DD</sub> x I<sub>D</sub>) and lattice temperature (T<sub>lattice</sub>), as shown in Eq. (1). Thermal resistance and lattice temperature decrease with an increase in L<sub>SELBOX</sub>. An

increase in LSELBOX results in an increase in the cross - section area for heat to dissipate into the substrate. In conventional JLT, the lattice temperature is lower compared to hybrid SELBOX - JLTs due to the former transistor's low drain current.

$$R_{TH} = \frac{(T_{lattice} - 300)}{P_{dissipated}}$$

(1)

**Figure 9:** Variation of lattice temperature for different  $L_{SELBOX}$  of HSJLT at  $L_{g} = 20$ nm,  $V_{DS} = 0.8$ V,  $V_{GS} = 0.8$ V.

**Figure 10:** Variation of thermal resistance for different  $L_{SELBOX}$  of HSJLT at  $L_{a} = 20$ nm,  $V_{DS} = 0.8$ V,  $V_{GS} = 0.8$ V.

From the simulation results discussed in section 3.1, it can be observed that the HSJLT exhibits a better performance at  $L_{SELBOX} \approx L_{g'}$  i.e., 20nm. It exhibits high  $I_{ON'}$  improved DIBL, and low  $R_{TH}$  when compared to conventional JLT.

#### 3.2 Analog Performance of HSJLT

This section presents the analog performance of HSJLT at  $L_{SELBOX} = 20$ nm. The analog figure of merits (FOM),

such as transconductance  $(g_m)$ , unity gain frequency  $(f_T)$ , transconductance generation factor (TGF), early voltage  $(V_{EA})$ , and intrinsic gain  $(A_0)$  of HSJLT, are compared with conventional and hybrid JLTs.

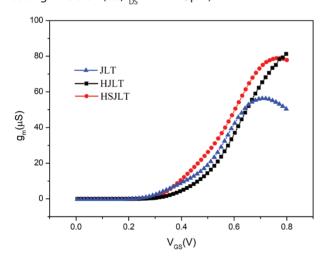

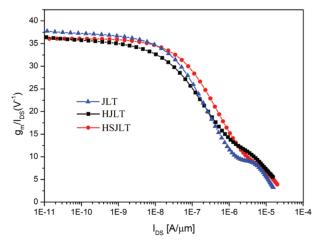

Figure 11 shows the transconductance variation concerning the change in the gate voltage of the three devices for the same  $I_{\rm OFF}$ . The transconductance of HSJLT is higher than conventional and hybrid JLTs because of the high-low field mobility of the former transistor. The higher the  $g_{\rm m}$ , the better the device's analog performance. Figure 12 shows the variation of the transconductance generation factor of the three devices with the change in  $I_{\rm DS}$ . TGF is the measure of the efficiency of the transistor to convert the drain current into transconductance; it also indicates the region of operation of the device [21]. From Figure 12, it can be observed that HSJLT exhibits a higher TGF than conventional and hybrid JLTs at the same drain current when the devices are in moderate or strong inversion (i.e.,  $I_{\rm DS} > 1\text{E-7 A/}\mu\text{m}$ ).

**Figure 11:** Transconductance variation of JLT, HJLT, and HSJLT with a change in the gate voltage.

**Figure 12:** TGF as a function  $I_{DS}/(W/L)$  in JLT, HJLT, and HSJLT.

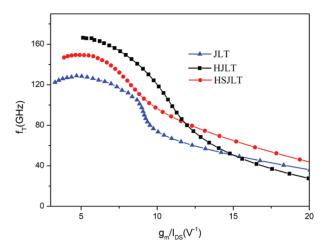

**Figure 13:** Variation of  $f_{\scriptscriptstyle T}$  as a function of TGF in JLT, HJLT, and HSJLT.

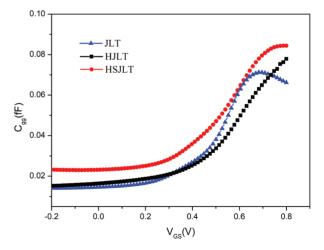

Figure 13 shows the variation of  $f_{\scriptscriptstyle T}$  as a function of  $g_{\scriptscriptstyle m}/I_{\scriptscriptstyle DS}$ .  $f_{\scriptscriptstyle T}$  depends on the total gate capacitance and transconductance, as shown in Eq. (2). HSJLT exhibits higher  $f_{\scriptscriptstyle T}$  than conventional JLT, but lower  $f_{\scriptscriptstyle T}$  than HJLT at moderate or strong inversion (i.e.,  $g_{\scriptscriptstyle m}/I_{\scriptscriptstyle DS} < 10$ ) due to the large gate capacitance of theHSJLT, as shown in Figure 14, and dipping of the transconductance. In deep-strong inversion (i.e.,  $10 < g_{\scriptscriptstyle m}/I_{\scriptscriptstyle DS} > 20$ ),  $f_{\scriptscriptstyle T}$  of HSJLT is higher when compared to the other two devices because of higher  $g_{\scriptscriptstyle m}$ .

$$f_{T} = \frac{g_{m}}{2\pi C_{gg}} = \frac{g_{m}}{I_{DS}} \cdot \frac{I_{DS}}{2\pi C_{gg}}$$

(2)

**Figure 14:** Gate capacitance dependence on the gate voltage in JLT, HJLT, and HSJLT.

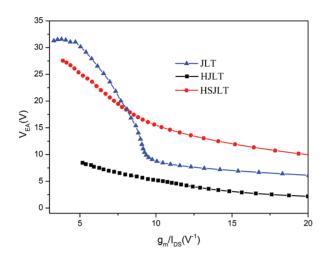

Figure 15 shows the variation of early voltage ( $V_{EA}$ ) as a function of TGF for JLT, HJLT, and HSJLTs.  $V_{EA}$  is the drain current - to - drain conductance ( $g_d$ ) ratio and is an important analog performance metric as it determines the transistor's intrinsic gain if TGF multiplies it.

**Figure 15:** Early voltage dependence on the TGF in JLT, HJLT, and HSJLT.

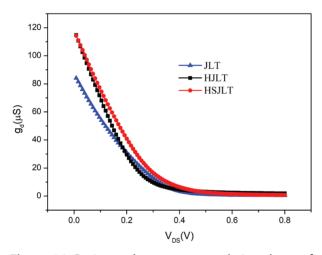

It can be observed from Figure 15 that in a moderate or strong inversion region, conventional JLT has larger  $V_{\text{EA}}$  than the HSJLT, because of the low drain conductance of the conventional JLT. In a deep-strong inversion region, HSJLT exhibits higher  $V_{\text{EA}}$  than conventional JLT, due to the high drain current and nearly the same drain conductance as shown in Figure 16.

**Figure 16:** Drain conductance versus drain voltage of JLT, HJLT, and HSJLT.

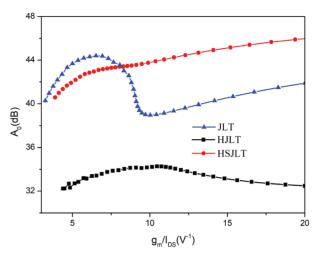

Figure 17 shows the variation of intrinsic gain ( $A_0$ ) as a function of TGF. Due to better transconductance generation factor and early voltage, conventional JLT provides high intrinsic gain compared to HSJLT in moderate or strong inversion region. HSJLT has a high intrinsic gain in the deep - strong inversion region than the other two devices.

**Figure 17:** Variation of intrinsic gain in JLT, HJLT, and HSJLT as a function of TGF.

#### 4 Conclusions

In this paper, the DC characteristics and the analog performance of the proposed HSJLT are presented. This paper illustrates the impact of variation in  $L_{\text{SELBOX}}$  of the proposed structure on the  $I_{\rm ON'}$   $I_{\rm OFF'}$  SS, DIBL, and thermal resistance. It is found from the simulation results that the proposed device architecture shows better DC performance for  $L_q \approx L_{SELBOX}$ . Within the same device area, the proposed device delivers 1.43 times higher drain current compared to conventional JLT due to combined technologies (UTB, FinFET, SELBOX). Simulation results show that the hybrid SELBOX- JLFinFET exhibits better immunity to self-heating when compared to conventional and hybrid JLFinFETs. The analog figure of merits, such as TGF, early voltage, and intrinsic gain, is evaluated through the simulations. It can be concluded from the simulation results that the hybrid SELBOX-JLFinFET is an option for high-performance applications due to higher  $I_{ON}$  and it exhibits better  $g_m/I_{D'}$   $f_{T'}$   $V_{EA}$  and intrinsic gain than the conventional and hybrid JLFinFETs.

## 5 References

- 1. Saremi, Mehdi, Behzad Ebrahimi, Ali Afzali Kusha, and Mohammad Saremi. "Process variation study of ground plane SOI MOSFET." In *Quality Electronic Design (ASQED), 2010 2nd Asia Symposium on*, pp. 66-69. IEEE, 2010.

- https://doi.org/10.1109/ASQED.2010.5548155

- Saremi, Mehdi, Masoumeh Saremi, Hamid Niazi, Maryam Saremi, and Arash Yazdanpanah Goharrizi. "SOI LDMOSFET with Up and Down Extended Stepped Drift Region." Journal of Electronic Materials 46, no. 10 (2017): 5570-5576.

- https://doi.org/10.1007/s11664-017-5645-z

- Li, Yiming, Hung-Mu Chou, and Jam-Wem Lee. "Investigation of electrical characteristics on surrounding-gate and omega-shaped-gate nanowire FinFETs." *IEEE Transactions on Nanotechnol*ogy 4, no. 5 (2005): 510-516. https://doi.org/10.1109/TNANO.2005.851410

- Hisamoto, Digh, Wen-Chin Lee, Jakub Kedzierski, Hideki Takeuchi, Kazuya Asano, Charles Kuo, Erik Anderson, Tsu-Jae King, Jeffrey Bokor, and Chenming Hu. "FinFET-a self-aligned double-gate

MOSFET scalable to 20 nm." IEEE Transactions on

Electron Devices 47, no. 12 (2000): 2320-2325. https://doi.org/10.1109/16.887014

5. Zhang, Weimin, Jerry G. Fossum, and Leo Mathew. "The ITFET: A novel FinFET-based hybrid device." *IEEE Transactions on Electron Devices* 53, no. 9 (2006): 2335-2343.

https://doi.org/10.1109/TED.2006.880813

- Fahad, Hossain M., Chenming Hu, and Muhammad M. Hussain. "Simulation study of a 3-D device integrating FinFET and UTBFET." IEEE Transactions on Electron Devices 62, no. 1 (2015): 83-87. https://doi.org/10.1109/TED.2014.2372695

- 7. Pradhan, K. P., and P. K. Sahu. "Exploration of symmetric high-k spacer (SHS) hybrid FinFET for high-performance application." Superlattices and Microstructures 90 (2016): 191-197. https://doi.org/10.1016/j.spmi.2015.12.005

- 8. Pradhan, K. P., M. G. C. Andrade, and P. K. Sahu. "Pros and cons of symmetrical dual-k spacer technology in hybrid FinFETs." *Superlattices and Microstructures* 100 (2016): 335-341. https://doi.org/10.1016/j.spmi.2016.09.043

- 9. Pradhan, K. P., and P. K. Sahu. "Study of fin tapering effect in nanoscale symmetric dual-k spacer (SDS) hybrid FinFETs." *Materials Science in Semiconductor Processing* 57 (2017): 185-189. https://doi.org/10.1016/j.mssp.2016.10.034

- Pradhan, K. P., and P. K. Sahu. "Investigation of asymmetric high-k underlap spacer (AHUS) hybrid FinFET from temperature perspective." Microsystem Technologies 23, no. 7 (2017): 2921-2926. https://doi.org/10.1007/s00542-016-2966-4

- Nelapati, Rajeev Pankaj, and K. Sivasankaran. "Impact of self-heating effect on the performance of hybrid FinFET." Microelectronics Journal 76 (2018): 63-68. <a href="https://doi.org/10.1016/j.mejo.2018.04.015">https://doi.org/10.1016/j.mejo.2018.04.015</a>

- 12. Colinge, Jean-Pierre, Chi-Woo Lee, Aryan Afzalian, Nima Dehdashti Akhavan, Ran Yan, Isabelle Ferain, Pedram Razavi et al. "Nanowire transistors without junctions." *Nature nanotechnology* 5, no. 3 (2010): 225.

- https://doi.org/10.1038/nnano.2010.15

- Han, Ming-Hung, Chun-Yen Chang, Hung-Bin Chen, Jia-Jiun Wu, Ya-Chi Cheng, and Yung-Chun Wu. "Performance comparison between bulk and

- SOI junctionless transistors." *IEEE Electron Device Letters* 34, no. 2 (2013): 169-171.

- https://doi.org/10.1109/LED.2012.2231395

- Zhang, Zheng Xuan, Qing Lin, Ming Zhu, and Cheng Lu Lin. "A new structure of SOI MOSFET for reducing self-heating effect." *Ceramics international* 30, no. 7 (2004): 1289-1293. https://doi.org/10.1016/j.ceramint.2003.12.033

- Raleva, K., D. Vasileska, A. Hossain, S-K. Yoo, and S. M. Goodnick. "Study of self-heating effects in SOI and conventional MOSFETs with electro-thermal particle-based device simulator." Journal of Computational Electronics 11, no. 1 (2012): 106-117. https://doi.org/10.1007/s10825-012-0384-0

- Narayanan, M. R., Hasan Al-Nashash, Baquer Mazhari, and Dipankar Pal. "Studies and minimization of kink effect in SOI MOSFET devices with SELBOX structure." In *Microelectronics*, 2008. ICM 2008. International Conference on, pp. 232-235. IEEE, 2008. https://doi.org/10.1109/ICM.2008.5393502

- 17. Khan, Uzma, Bahniman Ghosh, Md Waseem Akram, and Akshaykumar Salimath. "A comparative study of SELBOX-JLT and SOI-JLT." *Applied Physics A* 117, no. 4 (2014): 2281-2288. <a href="https://doi.org/10.1007/s00339-014-8661-3">https://doi.org/10.1007/s00339-014-8661-3</a>

- 18. Guide, Sentaurus Process User, and G. Version. "Synopsys." *Inc., Jun* (2012).

- Gundapaneni, Suresh, Swaroop Ganguly, and Anil Kottantharayil. "Bulk planar junctionless transistor (BPJLT):

An attractive device alternative for scaling." IEEE Electron Device Letters 32, no. 3 (2011): 261-263.

https://doi.org/10.1109/LED.2010.2099204

- 20. Guide, Sentaurus Device User, and G. Version. "Synopsys." *Inc., Jun* (2012).

- Silveira, Flandre, Denis Flandre, and P. G. A. Jespers. "gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA." IEEE Journal of Solid-State Circuits 31, no. 9 (1996): 1314-1319.

https://doi.org/10.1109/4.535416

Copyright © 2019 by the Authors. This is an open access article distributed under the Creative Com-

mons Attribution (CC BY) License (https://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Arrived: 01. 11. 2018 Accepted: 26. 03. 2019