https://doi.org/10.33180/InfMIDEM2019.305

Journal of Microelectronics, Electronic Components and Materials Vol. 49, No. 3(2019), 169 – 176

## Novel Dual Mode Multifunction Filter Employing Highly Versatile VD-DXCC

Musa Ali Albrni<sup>1</sup>, Mohammad Faseehuddin<sup>1</sup>, Jahariah Sampe<sup>1</sup>, Sawal Hamid Md Ali<sup>2</sup>

<sup>1</sup>University Kebangsaan Malaysia (UKM), Institute of Microengineering and Nanoelectronics (IMEN), Bangi, Selangor, Malaysia.

<sup>2</sup>University Kebangsaan Malaysia (UKM), Faculty of Engineering & Built Environment, UKM, Department of Electrical, Electronic and Systems Engineering, Bangi, Selangor, Malaysia.

**Abstract:** In this research a new highly versatile analog building block (ABB), the voltage differencing dual X current conveyor (VD-DXCC), is proposed. It is employed to synthesize a versatile dual mode biquadratic filter. The proposed filter uses canonical number of passive elements and has inbuilt tunability feature. In addition, the proposed filter can work as multi input single output (MISO) and single input multi output (SIMO) filter in current mode (CM) of operation. Furthermore, the quality factor and pole frequency of the filter can be set independently. The non-ideal gain analysis and sensitivity analysis of the filters is also carried out to study the effect of process variations and process spread on the filter response. The proposed designs are validated using 0.18 um Silterra Malaysia process design kit (PDK) in Cadence Virtuoso design software. The parasitic extraction is carried out using Calibre tool from Mentor Graphics. The complete layout of the VD-DXCC is made and post layout simulation results are given for each design. The post layout results are in close agreement with the theoretical analysis.

Keywords: biomedical signal processing, current mode; current conveyor; filter; voltage mode

## Nov multifunkcijski filter z dvojnim delovanjem v visoko prilagodljivem VD-DXCC

**Izvleček:** V članku je predstavljen nov visoko prilagodljiv analogni blokovni napetostno diferenčni tokovni ojačevalnik (VD-DXCC), ki vsebuje prilagodljiv bi-kvadratni filter. Filter vsebuje kanonično število pasivnih komponent in ima sposobnost nastavljanja. Filter lahko deluje v več-vhodnem eno-izhodnem ali eno-vhodnem več-izhodnem načinu. Model je preverjen v 0.18 um Silterra Malaysia načrtovalskem kitu in programskem paketu Cadence Virtuoso. Rezultati izdelave se ujemajo s teoretično analizo.

Ključne besede: biomedicinsko procesiranje signalov; tokovni način; tokovni ojačevalnik; filter; napetostni način

\* Corresponding Author's e-mail: jahariah@ukm.edu.my

## 1 Introduction

Analog circuits play a vital role in all electronic systems. The analog circuits are used for interfacing analog world with the digital systems or as standalone high speed signal conditioning systems. The analog signal processing (ASP) offers tremendous benefits over digital signal processing (DSP), especially in terms of chip area, power consumption and speed [1]. All naturally occurring signals are analog in nature, in order to process them digitally the signals need to be converted from analog domain to digital domain and back to analog domain after processing. The digital signal processors require the extra analog to digital converter (ADC) and digital to analog converter (DAC) together with interfacing circuits this increases the power and area requirement of digital signal processing. Recently, the current mode analog active blocks are widely utilized by the researchers in designing analog filters due their advantages over voltage mode circuits [2-3]. The most utilized current mode active blocks are the second generation current conveyor (CCII) [1], differential difference current conveyor (DDCC) [2], fully differential current conveyor (FDCCII) [11], current feedback operational amplifier (CFOA) [1], current backward transconductance amplifier (CBTA) [8], current conveyor transconductance amplifier (CCTA) [22], differential voltage current conveyor (DVCCII) [10], voltage differencing current conveyor (VDCCII) [11], differential voltage current conveyor transconductance amplifier (DVCCTA) [15] etc. Each block carries its own advantages in context to the same the authors in this paper propose another versatile ABB namely the voltage differencing dual X current conveyor (VD-DXCC).

Filters are a critical part of any electronics system. They are employed in data acquisition systems, communication equipment, phase shifters, oscillator designs and bio-medical devices etc. [1, 19]. Portable and network connected medical devices for real time monitoring and diagnosis of diseases will be vital in detecting diseases for future medical observation system. To develop such a system low power and low noise analog circuits such as amplifiers and filters are required for physiological signal acquisition and signal processing. The filters are also vital parts in bio-medical data acquisition systems like sensors for artificial kidney for blood flow and filtration rate detection etc. The universal filters are most versatile as they can provide low pass (LP), high pass (HP), notch pass (NP), band pass (BP) and all pass (AP) responses from a single configuration. The main attributes that are desirable in any filter structure are (i) tunability (ii) use of minimum number of passive elements (iii) no requirement of matching between passive components (iv) provision of independent tunability of pole frequency and quality factor (v) use of minimum number of active blocks. The Table 1 provides a detailed literature survey of some exemplary MISO filters from the literature. The study points out that most of the designs suffer from one of the following issues (i) excessive use of active blocks and passive components (ii) lack of tunability (iii) requirement of passive component matching (iv) need of inverting input signal for the realization of filter function.

In this research a highly versatile ABB the VD-DXCC is developed and utilized in design of a MISO dual mode universal filter and SIMO CM filter. The proposed circuits utilized one ABB and minimum passive components. The designed circuits are electronically tunable via bias current of the OTA. The proposed circuits are

| S. No.   | Mode of<br>Operation         | Active<br>Block<br>Used(No.) | No. of<br>R+C | No. of<br>grounded<br>C+R | Matching<br>Condition           | Electronic<br>Tunability | Inverting<br>Input<br>Needed | Low output<br>Impedance | Power<br>Dissipation         |

|----------|------------------------------|------------------------------|---------------|---------------------------|---------------------------------|--------------------------|------------------------------|-------------------------|------------------------------|

| [20]     | MISO (VM)                    | CCII+ (3)                    | 2+2           | 0+0                       | No                              | No                       | No<br>(Except<br>for AP)     | No                      | -                            |

| [21]     | MISO<br>(VM)                 | DVCC (3)                     | 4+2           | 2+3                       | No<br>(Except<br>for AP)        | No                       | No                           | No                      | 4.266 mW                     |

| [22]     | MISO<br>(VM)                 | CCTA (1)                     | 2+2           | 0+0                       | No                              | Yes                      | No                           | No                      | -                            |

| [23]     | MIMO<br>(VM)                 | DVCC (1)                     | 2+2           | 0+0                       | Yes                             | No                       | No                           | No                      | -                            |

| [24]     | MISO<br>(VM)                 | DOCCCII<br>(2)               | 0+2           | 0+0                       | No                              | Yes                      | No<br>(Except<br>for AP)     | No                      | -                            |

| [25]     | MISO<br>(VM)                 | VD-DIBA                      | 1+2           | 0+0                       | No                              | Yes                      | No                           | No                      | -                            |

| [26]     | MISO<br>(VM)                 | CDBA (2)                     | 4+2           | 0+0                       | Yes                             | No                       | No                           | Yes                     | -                            |

| [27]     | MISO<br>(VM)                 | DDCC (2)                     | 2+2           | 2+1                       | No                              | No                       | No                           | No                      | -                            |

| [28]     | MIMO<br>(VM)                 | FDCCII (1)                   | 3+2           | 1+1                       | No                              | No                       | No<br>(Except<br>for AP)     | No                      | -                            |

| [29]     | MISO<br>(VM)                 | DDCC (3)                     | 2+2           | 2+2                       | No                              | No                       | No                           | Yes                     | -                            |

| [30]     | MISO (VM)                    | CCII (2)                     | 3+2           | 0+0                       | Yes                             | No                       | Yes                          | Yes                     | 3.65 mW                      |

| Proposed | MISO(VM<br>& CM)/<br>SIMO CM | VD-DXCC<br>(1)               | 2+2           | 1+0                       | No<br>(except<br>in MISO<br>CM) | Yes                      | No                           | Yes                     | 2.237 Mw<br>(for VM<br>Mode) |

Table 1: Comparison of MISO filters available in the literature with the proposed filter

validated using 0.18µm PDK from Silterra Malaysia in Cadence to verify the theoretical predictions.

# 2 Voltage differencing dual X current conveyor

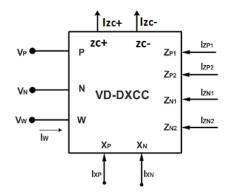

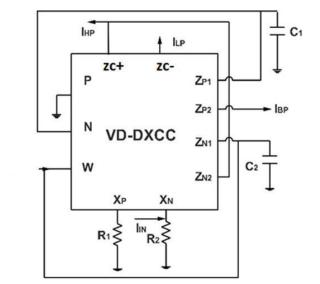

The block diagram of VD-DXCC is shown in Figure 1 and the current voltage equations are presented in matrix Equation 1. The VD-DXCC is a two stage ABB. The first stage consists of operational transconductance amplifier (OTA) and second stage is dual X current conveyor (DXCC).

Figure 1: Block diagram of VD-DXCC

| $\begin{bmatrix} I_N \end{bmatrix}$ |   | г0    | 0      | 0  | 0 | 0 | 0 | 0      | 0      | $0$ ן $V_P$ ן                                                                                                            |

|-------------------------------------|---|-------|--------|----|---|---|---|--------|--------|--------------------------------------------------------------------------------------------------------------------------|

| $I_P$                               |   | 0     | 0      | 0  | 0 | 0 | 0 | 0      | 0      | $0 V_N$                                                                                                                  |

| $I_{zc\pm/I_W}$                     |   | $g_m$ | $-g_m$ | 0  | 0 | 0 | 0 | 0      | 0      | $0 V_W$                                                                                                                  |

| $V_{XP}$                            |   | 0     | 0      | 1  | 0 | 0 | 0 | 0      | 0      | $0 \mid I_{XP} \mid$                                                                                                     |

| $V_{XN}$                            | = | 0     | 0      | -1 | 0 | 0 | 0 | 0      | 0      | $0 \mid I_{XN} \mid (1)$                                                                                                 |

| $I_{ZP1}$                           |   | 0     | 0      | 0  | 1 | 0 | 0 | 0      | 0      | $0 \mid V_{ZP1}$                                                                                                         |

| $I_{ZP2}$                           |   | 0     | 0      | 0  | 1 | 0 | 0 | 0      | 0      | $0 \mid V_{ZP2}$                                                                                                         |

| $I_{ZN1}$                           |   | 0     | 0      | 0  | 0 | 1 | 0 | 0      | 0      | $0 V_{ZN1}$                                                                                                              |

| $I_{ZN2}$                           |   | Γ0    | 0      | 0  | 0 | 1 | 0 | 0      | 0      | $0 \left[ V_{ZN2} \right]$                                                                                               |

| $I_{ZP2}$                           |   | 0     | 0<br>0 | 0  |   |   | 0 | 0<br>0 | 0<br>0 | $\begin{bmatrix} V_{ZP1} \\ V_{ZP2} \\ 0 \\ V_{ZN1} \\ 0 \end{bmatrix} \begin{bmatrix} V_{ZN1} \\ V_{ZN2} \end{bmatrix}$ |

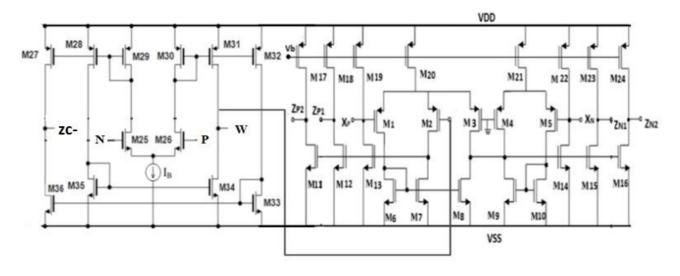

The CMOS implementation of VD-DXCC is presented in Figure 2. The transistors (M25-M36) form the OTA which is the first stage of the VD-DXCC. The output current of the OTA depends on the voltage difference between voltages at terminals *P* and *N*. Assuming saturation region operation for all transistors and equal W/L ratio for transistors M25 and M26 the output current  $I_{zc^{\pm}} = I_{W}$  of the OTA is given by Equation 2. The **ZC** $\pm$  terminals are high impedance current output terminals.

$$\boldsymbol{I}_{ZC^{\pm}} = \boldsymbol{I}_{W} = \boldsymbol{g}_{m} \left( \boldsymbol{V}_{P} - \boldsymbol{V}_{N} \right) = \left( \sqrt{2 \boldsymbol{I}_{Bias} \boldsymbol{k}_{i}} \right) \left( \boldsymbol{V}_{P} - \boldsymbol{V}_{N} \right)$$

(2)

Where,  $K_i = \mu C_{ox} W/2L$  (i=25, 26), W is the effective channel width, L is the effective length of the channel,  $C_{ox}$  is the gate oxide capacitance per unit area and  $\mu$  is the carrier mobility.

The second stage consists of transistors (M1-24). The W terminal is high impedance voltage input terminal, the  $X_p$  and  $X_N$  terminals are low impedance current input terminals and the  $Z_{p1-2}$ ,  $Z_{N1-2}$ , terminals are high impedance current output terminals.

#### 3 Layout design

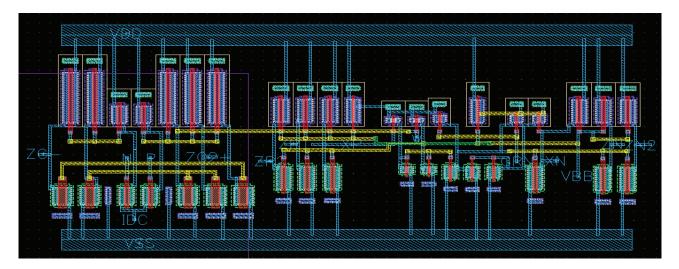

The complete layout of the VD-DXCC is designed using Silterra Malaysia 0.18µm PDK in cadence design suit. The high performance nhp and php MOS transistors are used for the design. To minimize the effect of parasitics the transistors are put as close as possible. Three level of metal layers are used for the interconnections. The complete layout is presented in Figure 3. The layout occupies an area of  $(55*25.73\mu m^2)$ .

Figure 2: CMOS Implementation of VD-DXCC

Figure 3: Layout of the VD-DXCC

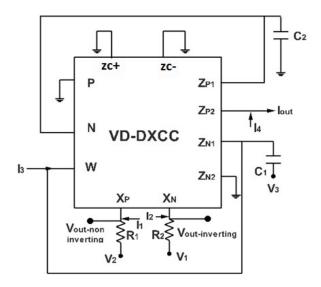

## 4 Proposed dual mode universal filter

The proposed dual mode MISO filter is presented in Figure 4. The filter consists of four passive elements and can work in VM and CM without requiring any changes in its topology. Furthermore, the proposed filter with addition of some extra output terminals can function as CM SIMO filter as well. The features of the filter include ability to work in dual modes, no requirement of negative inputs for realization of filter functions, orthogonal control of frequency and quality factor, simultaneous availability of inverting and non-inverting outputs in the VM configuration, availability of current output at high impedance node, no matching between passive elements is required (except in CM MISO configuration) and tunability. The operation of filter in MISO and SIMO configurations is discussed below:

Figure 4: Dual mode MISO universal filter

4.1 Voltage Mode Operation in MISO Configuration

In this mode of operation, the input currents  $I_1$  to  $I_4$  are set to zero. The input voltage  $V_1$  to  $V_3$  are applied according to Table 2 to realize a given filter response. In the design capacitor  $C_2$  is always grounded which is beneficial for integrated circuit implementation. Structures using grounded capacitors are advantageous with respect to reducing parasitic effects and the chip area, as the floating capacitor has bigger parasitic capacitances and requires larger chip area [31-32]. The output of the filter can be obtained from low impedance  $X_p$  and  $X_N$  nodes. This filter provides both inverting and non-inverting output signals which is another striking feature of the design. The filter transfer function and expression for frequency are given in Equations (3-5).

$$V_{out} = \frac{S^2 V_3 C_1 C_2 R_1 R_2 - s R_1 C_2 V_1 + g_m R_2 V_2}{S^2 C_1 C_2 R_1 R_2 + s C_2 R_1 + R_2 g_m}$$

(3)

$$\omega_o = \sqrt{\frac{g_m}{C_1 C_2 R_1}} \tag{4}$$

$$Q = R_2 \sqrt{\frac{g_m C_1}{C_2 R_1}} \tag{5}$$

Table 2: Input Excitation Sequence for VM

| Response |                       | Inputs         |       | Matching Required |  |  |

|----------|-----------------------|----------------|-------|-------------------|--|--|

|          | <b>V</b> <sub>1</sub> | V <sub>2</sub> | $V_3$ | No                |  |  |

| LP       | 0                     | 0              | 1     | No                |  |  |

| HP       | 1                     | 0              | 0     | No                |  |  |

| BP       | 0                     | 1              | 0     | No                |  |  |

| NP       | 1                     | 0              | 1     | No                |  |  |

| AP       | 1                     | 1              | 1     | No                |  |  |

#### 4.2 Current Mode Operation in MISO Configuration

In CM operation the input voltages  $V_1$  to  $V_3$  are reduced to zero grounding all the passive elements. The input current  $I_1$  to  $I_4$  are applied according to Table 3 to realize a given filter response. As can be deduced from the filter structure the output current is obtained from high output impedance terminal which is necessary for cascading. The filter requires a simple resistive matching condition for realizing HP, NP and AP responses. The slight drawback is the requirement of double input to realize AP response but given the capability of the filter to work in dual mode this can be accommodated. The transfer function and expression for frequency are given Equation (6-8).

$$\frac{I_{LP}}{I_{IN}} = -\frac{g_m R_2}{S^2 C_1 C_2 R_1 R_2 + s C_2 R_1 + R_2 g_m}$$

(10)

$$\frac{I_{BP}}{I_{IN}} = -\frac{sC_2R_1}{S^2C_1C_2R_1R_2 + sC_2R_1 + R_2g_m}$$

(11)

$$\omega_o = \sqrt{\frac{g_m}{C_1 C_2 R_1}} \tag{12}$$

$$Q = R_2 \sqrt{\frac{g_m C_2}{C_1 R_1}} \tag{13}$$

$$I_{out} = \frac{(S^2 C_1 C_2 R_1 R_2 + s R_1 C_2 + g_m R_2) I_4 - ((S^2 C_1 C_2 R_1 R_2 + s R_1 C_2) I_1}{-s R_2 C_2 I_2 + s R_2 C_2 I_3}$$

(6)

$$\omega_o = \sqrt{\frac{g_m}{C_1 C_2 R_1}} \tag{7}$$

$$Q = R_2 \sqrt{\frac{g_m C_1}{C_2 R_1}} \tag{8}$$

Table 3: Input Excitation Sequence for CM

| Response |                | Matching<br>Required |                |                       |                         |

|----------|----------------|----------------------|----------------|-----------------------|-------------------------|

|          | I <sub>1</sub> | l <sub>2</sub>       | I <sub>3</sub> | <b>I</b> <sub>4</sub> |                         |

| LP       | 1              | 0                    | 0              | 1                     | No                      |

| HP       | 1              | 1                    | 0              | 0                     | $R_1 = R_2$             |

| BP       | 0              | 0                    | 1              | 0                     | No                      |

| NP       | 0              | 1                    | 0              | 1                     | $R_1 = R_2$ $R_1 = R_2$ |

| AP       | 0              | 2                    | 0              | 1                     | $R_1 = R_2$             |

4.3 Current Mode Operation in SIMO Configuration

The SIMO filter structure is shown in Figure 5. As can be seen from the figure the filter has same topology as the previously discussed dual mode MISO filter presented in Figure 4. This topology has additional output terminals to provide explicit current output from high impedance nodes. The filter transfer function and expression for pole frequency and quality factor are summarized in Equations 9-13.

$$\frac{I_{HP}}{I_{IN}} = -\frac{S^2 C_1 C_2 R_1 R_2}{S^2 C_1 C_2 R_1 R_2 + s C_2 R_1 + R_2 g_m}$$

(9)

Figure 5: SIMO filter structure

# 5 Non-ideal gain and sensitivity analysis

In this section the non-idealities of the VD-DXCC are considered and their influence on the proposed filter circuits is analyzed. The frequency dependent non-ideal voltage ( $\beta$ ), current ( $\alpha$ ) and transconductance transfer ( $\gamma/\gamma'$ ) gains cause a slight change in the current and voltage signals during transfer leading to undesired response. Considering the effect of frequency dependent current and voltage transfer gains the V-I characteristics of VD-DXCC are modified as given below.

$$I_{ZP1} = I_{ZP2} = \alpha_P I_{XP} \tag{14}$$

$$I_{ZN1} = I_{ZN2} = \alpha_N I_{NP} \tag{15}$$

$$V_{XN} = -\beta_N V_W \tag{16}$$

$$V_{XP} = \beta_P V_W \tag{17}$$

$$\boldsymbol{I}_{\boldsymbol{ZC}+} = \boldsymbol{I}_{\boldsymbol{W}} = \boldsymbol{\gamma}' \boldsymbol{g}_1 \left( \boldsymbol{V}_{\boldsymbol{P}} - \boldsymbol{V}_{\boldsymbol{N}} \right)$$

(18)

$$\boldsymbol{I}_{\boldsymbol{Z}\boldsymbol{C}-} = -\gamma \boldsymbol{g}_1 \left( \boldsymbol{V}_{\boldsymbol{P}} - \boldsymbol{V}_N \right) \tag{19}$$

Where  $\alpha$  is the current transfer gain,  $\beta$  stands for voltage transfer gain and  $\gamma$  denotes the transconductance transfer gain. Ideally their values should be unity.

The transfer function, pole frequency and quality factor of the MISO filter considering the effect of non-ideal current and voltage gains are given in Equations (20-23).

$$-S_{C_1}^{\omega} = -S_{C_2}^{\omega} = -S_{R_1}^{\omega} = S_{\gamma'}^{\omega} = S_{g_1}^{\omega} = S_{\alpha_P}^{\omega} = S_{\beta_P}^{\omega} = \frac{1}{2}$$

(26)

$$-S_{C_1}^{\mathcal{Q}} = -S_{R_1}^{\omega} = S_{C_2}^{\mathcal{Q}} = -S_{R_2}^{\mathcal{Q}} = S_{g_1}^{\mathcal{Q}} = S_{\alpha_p}^{\mathcal{Q}} = S_{\beta_p}^{\mathcal{Q}} = S_{\gamma'}^{\mathcal{Q}} = \frac{1}{2}$$

(27)

$$S_{R_2}^Q = 1 \tag{28}$$

$$-S_{C_1}^{\omega} = -S_{C_2}^{\omega} = -S_{R_1}^{\omega} = S_{\gamma'}^{\omega} = S_{\beta_p}^{\omega} = S_{g_1}^{\omega} = S_{\alpha_p}^{\omega} = \frac{1}{2}$$

(29)

$$S_{C_2}^{Q} = -S_{C_1}^{Q} = S_{\alpha_p}^{Q} = -S_{R_1}^{\omega} = S_{\gamma'}^{Q} = S_{\beta_p}^{Q} = S_{g_1}^{\omega} = \frac{1}{2}$$

(30)

$$S_{R_2}^Q = 1 \tag{31}$$

### 6 Simulation results

To validate the proposed designs the VD-DXCC is designed in  $0.18\mu m$  PDK from Silterra Malaysia. The com-

$$V_{out} = \frac{S^2 C_1 C_2 R_1 R_2 V_3 - \alpha_N S C_2 R_1 V_1 + \gamma' \alpha_P g_1 R_2 V_2}{S^2 C_1 C_2 R_1 R_2 + \alpha_N \beta_N S C_2 R_1 + \gamma' \alpha_P \beta_P g_1 R_2}$$

(20)

$$I_{out} = \frac{-\alpha_{P}\alpha_{N}\beta_{P}SC_{2}R_{1}R_{2} + \alpha_{N}\beta_{N}SC_{2}R_{1} + \gamma'\alpha_{P}\beta_{P}g_{1}R_{2})I_{4}}{S^{2}C_{1}C_{2}R_{1}I_{2} + \alpha_{P}\beta_{P}SC_{2}R_{2}I_{3} - \alpha_{P}(S^{2}C_{1}C_{2}R_{1}R_{2} + \alpha_{N}\beta_{N}SC_{2}R_{1})I_{1}}{S^{2}C_{1}C_{2}R_{1}R_{2} + \alpha_{N}\beta_{N}SC_{2}R_{1} + \gamma'\alpha_{P}\beta_{P}g_{1}R_{2}}$$

(21)

$$\omega_o = \sqrt{\frac{\gamma' \alpha_P \beta_P g_1}{C_1 C_2 R_1}} \tag{22}$$

$$Q = R_2 \sqrt{\frac{\gamma' \alpha_P \beta_P g_1 C_1}{C_2 R_1}}$$

(23)

The non-ideal expressions for pole frequency and quality factor of the SIMO filter are presented in Equations (24-25).

$$\omega_o = \sqrt{\frac{\alpha_P \beta_P \gamma' g_m}{C_1 C_2 R_1}}$$

(24)

$$Q = R_2 \sqrt{\frac{\alpha_P \beta_P \gamma' g_m C_1}{C_2 R_1}}$$

(25)

The sensitivities of  $\omega_{o}$  and Q with respect to the nonideal gain and passive elements are given below. The Equations (26-28) give sensitivities of MISO filter and Equations (29-31) give sensitivities of SIMO filter. The sensitivities are not more than one which is desired. plete layout of the VD-DXCC is designed and the post layout results are discussed. The transistors width and length used are presented in Table 4. The circuits are simulated at a supply voltage of  $V_{DD} = -V_{SS} = 1.25$ V. The transconductance of OTA is fixed at  $g_m = 903.92\mu$ S by selecting bias current of OTA,  $I_B = 100\mu$ A. The current and voltage transfer gains are found to be ( $\alpha$ =0.976 and  $\beta$ =0.982).

Table 4: Width and length of the transistors

| Transistor | Width (W µm) | Length(L µm) |  |  |

|------------|--------------|--------------|--|--|

| M1- M2     | 1.4          | 0.7          |  |  |

| M3- M5     | 2.8          | 0.7          |  |  |

| M6- M7     | 2.4          | 0.7          |  |  |

| M8- M10    | 4.8          | 0.7          |  |  |

| M11-M24    | 9.6          | 0.7          |  |  |

| M25-M36    | 2            | 1            |  |  |

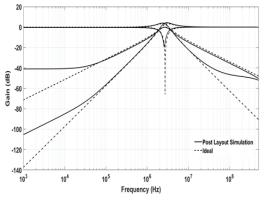

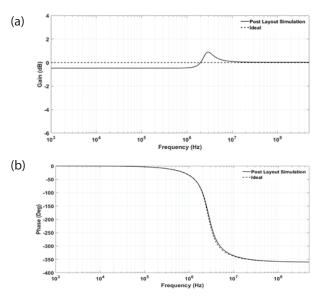

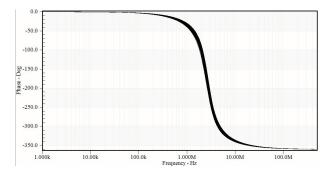

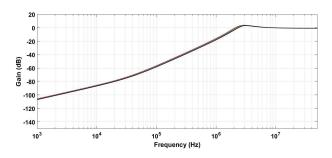

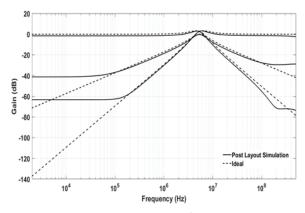

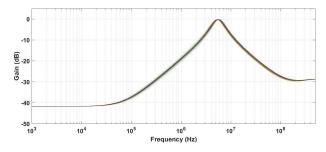

The dual mode filter is validated by designing it for a frequency of 2.704 MHz in voltage mode of operation. The passive elements are selected as  $R_1 = 4k\Omega$ ,  $R_2 = 4k\Omega$ ,  $C_1 = 20$  pF,  $C_2 = 20$  pF and  $I_{Bias} = 20$  uA. The ideal and post

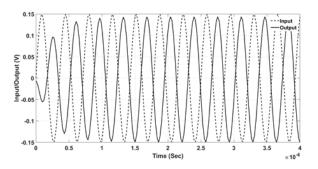

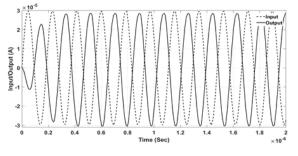

layout response of the filter is shown in Figures 6-7. The simulated pole frequency of the filter is found to be 2.7959 MHz which translates into 3.4% error. To examine the signal processing capability of the filter transient analysis is performed for band pass configuration. A sinusoidal signal of 100mV amplitude and 2.704 MHz frequency is given at the input and the output is noted. It can be deduced from Figure 8 that the filter functions well.

Figure 6: Frequency response of VM Filter

Figure 7: Frequency response of VM AP Filter

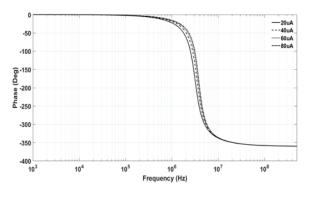

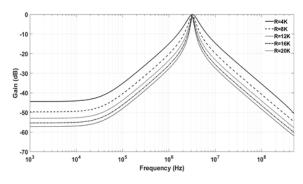

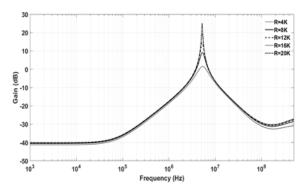

The tunability feature of the filter is verified. First, the filtering frequency is varied by changing the bias current of the VD-DXCC as shown in Figure 9. Second, the quality factor is varied by changing the value of the resistor  $R_2$  as presented in Figure 10. It can be seen that the frequency and quality factor of the filter can be independently controlled. The power dissipation of the filter for VM is found to be 2.237mW.

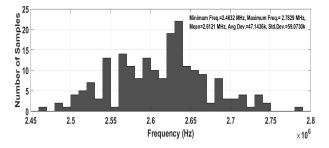

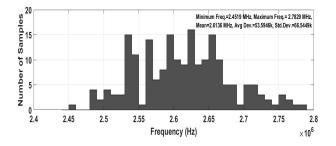

To study the effect of process variation on the proposed filter Monte Carlo analysis is carried out for 10% variation in capacitors ( $C_1 \& C_2$ ) values for the AP response.

Figure 8: Transient analysis of BP filter

Figure 9: Frequency response tunability of VM Filter

Figure 10: Quality factor tunability of VM Filter

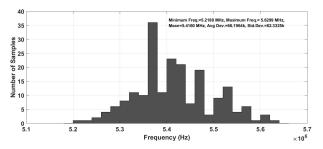

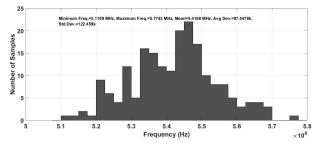

The analysis is done for 200 runs and the results are presented in Figures 11-12. To further examine the filter the Monte Carlo analysis is done for 10% variation in capacitor ( $C_1 \& C_2$ ) and resistors ( $R_1 \& R_2$ ) values for 200 runs for HP response. The results are presented in Figures 13-14. The analysis results indicate that the filter performs well and requires no matching of passive elements.

Now the CM mode operation in MISO configuration is investigated. The filter is designed for a frequency of 5.408 MHz. The passive elements are selected as R<sub>1</sub> =  $4k\Omega$ , R<sub>2</sub> =  $4k\Omega$ , C<sub>1</sub> = 10pF, C<sub>2</sub> = 10pF and I<sub>Bias</sub> = 20uA. The response of the filter is shown in Figures 15. The quality factor tunability is also tested for different values of the resistor *R2* as presented in Figure 16. It can be inferred

Figure 11: The Monte Carlo analysis results for AP response

Figure 12: The Monte Carlo analysis results for AP phase

Figure 13: The Monte Carlo analysis results for HP response

Figure 14: The Monte Carlo analysis results for HP response

from the figure that the quality factor can be tuned independent of the frequency. The transient analysis result for BP configuration are also presented in Figure 17 which further testifies the accurate signal processing capability of the filter structure.

Figure 15: Frequency response of CM SIMO Filter

Figure 16: Quality factor tunability of CM SIMO Filter

Figure 17: Transient analysis of BP SIMO filter configuration

Figure 18: The Monte Carlo analysis results for BP response

The Monte Carlo analysis is carried out for the CM SIMO filter for 10% variation in resistors (R<sub>1</sub>&R<sub>2</sub>) values

for BP response. The analysis is done for 200 runs and the results are presented in Figures 18-19. Additionally, Monte Carlo analysis is also done for 10% variation in capacitors ( $C_1 \& C_2$ ) values. The results are given in Figure 20. It can be inferred from the analysis results that the filter does not require an passive components matching constraints.

Figure 19: The Monte Carlo analysis results BP response

Figure 20: The Monte Carlo analysis results for BP filter response

### 7 Acknowledgement

This work is funded by Minister of Education Malaysia under grant FRGS/1/2018/TK04/UKM/02/1 and AKU254:HICoE (Fasa II) 'MEMS for Biomedical Devices (artificial kidney)'.

## 8 Conclusion

In this research, a newly proposed ABB the VD-DXCC is employed in designing a novel dual mode filter capable of working in MISO (VM, CM) and SIMO (CM) configurations. The developed filter did not require any passive components matching condition (except in SIMO CM configuration) for realizing filter responses. The pole frequency and quality factor of the proposed filter can be tuned independently. The non-ideal and sensitivity analysis are also carried out for the filter circuit to study the effect of the process variations. The post layout simulations are in close agreement with the theoretical analysis.

## 9 Reference

- Ferri, G., & Guerrini, N. C. (2003). Low-voltage lowpower CMOS current conveyors. Springer Science & Business Media. <u>https://doi.org/10.1007/b105853</u>

- 2. İbrahim, M. A., Minaei, S., Yüce, E., Herencsar, N., & Koton, J. (2012). Lossy/lossless floating/grounded inductance simulation using one DDCC.

- 3. Yuce, E. (2006). Floating inductance, FDNR and capacitance simulation circuit employing only grounded passive elements. *International Journal of Electronics*, *93*(10), 679-688. https://doi.org/10.1080/00207210600750208

- 4. Metin, B., & Cicekoglu, O. (2006). A novel floating lossy inductance realization topology with NICs using current conveyors. *IEEE Transactions On Circuits And Systems II: Express Briefs*, *53*(6), 483-486. <u>https://doi.org/10.1109/TCSII.2006.873826</u>

- Yuce, E., Cicekoglu, O., & Minaei, S. (2006). CCIIbased grounded to floating immittance converter and a floating inductance simulator. *Analog integrated circuits and signal processing*, 46(3), 287-291.

- https://doi.org/10.1007/s10470-006-1624-7

- Senani, R. (1986). On the realization of floating active elements. *IEEE transactions on circuits and* systems, 33(3), 323-324. https://doi.org/10.1109/TCS.1986.1085896

- Kiranon, W., & Pawarangkoon, P. (1997). Floating inductance simulation based on current conveyors. Electronics letters, 33(21), 1748-1749. <u>https://doi.org/10.1049/el:19971202</u>

- Ayten, U. E., Sagbas, M., Herencsar, N., & Koton, J. (2012). Novel floating general element simulators using CBTA. *Radioengineering*, *21*(1), 11-19.

- Sagbas, M. (2011). Component reduced floating±L,±C and±R simulators with grounded passive components. AEU-International Journal of Electronics and Communications, 65(10), 794-798. https://doi.org/10.1016/j.aeue.2011.01.006

- Manhas, P. S., & Pal, K. (2011). A low voltage active circuit for realizing floating inductance, capacitance, frequency dependent negative resistances and admittance converter. *Arabian Journal for Science and Engineering*, *36*(7), 1313-1319. https://doi.org/10.1007/s13369-011-0107-z

- Kartci, A., Ayten, U. E., Herencsar, N., Sotner, R., Jerabek, J., & Vrba, K. (2015). Application possibilities of VDCC in general floating element simulator circuit. In *European Conference on Circuit Theory and Design (ECCTD)* (pp. 1-4).

https://doi.org/10.1109/ECCTD.2015.7300064

12. Prommee, P., & Somdunyakanok, M. (2011). CMOS-based current-controlled DDCC and its applications to capacitance multiplier and universal filter. *AEU-International Journal of Electronics and Communications*, 65(1), 1-8.

https://doi.org/10.1016/j.aeue.2009.12.002

- Güney, A., & Kuntman, H. (2014). New floating inductance simulator employing a single ZC-VDTA and one grounded capacitor. In 9th IEEE International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS) (pp. 1-2). https://doi.org/10.1109/DTIS.2014.6850643

- 14. Channumsin, O., Pimpol, J., Thongsopa, C., & Tangsrirat, W. (2015, October). VDBA-based floating inductance simulator with a grounded capacitor. In 7th International Conference on Information Technology and Electrical Engineering (ICITEE) (pp. 114-117).

https://doi.org/10.1109/ICITEED.2015.7408924

- 16. Singh, A. K., Kumar, P., & Senani, R. (2018). Electronically tunable grounded/floating inductance simulators using Z-copy CFCCC. *Turkish Journal of Electrical Engineering & Computer Sciences, 26*(2), 1041-1055.

https://doi.org/10.3906/elk-1703-230

- Mohammad, F., Sampe, J., Shireen, S., & Ali, S. H. M. (2017). Minimum passive components based lossy and lossless inductor simulators employing a new active block. *AEU-International Journal of Electronics and Communications*, 82, 226-240. <u>https://doi.org/10.1016/j.aeue.2017.08.046</u>

- Sampe, J., Faseehuddin, M., Majlis, B. Y., Ali, S. H. M., & Yusoff, Z. (2017). Grounded and floating impedance simulators employing a new active element. In *IEEE Regional Symposium on Micro and Nanoelectronics (RSM)*pp. 58-61. https://doi.org/10.1109/RSM.2017.8069112

- Mohan, P. A. (2012). Current-mode VLSI analog filters: design and applications. Springer Science & Business Media <u>https://doi.org/10.1007/978-1-4612-0033-8</u>

- Horng, J. W. (2001). High-input impedance voltage-mode universal biquadratic filter using three plus-type CCIIs. *IEEE Transactions on Circuits* and Systems II: Analog and Digital Signal Processing, 48(10), 996-997.

https://doi.org/10.1109/82.974791

- 21. Horng, J. W., Hsu, C. H., & Tseng, C. Y. (2012). High input impedance voltage-mode universal biquadratic filters with three inputs using three CCs and grounding capacitors. *Radioengineering*, *21*(1), 290-296.

- 22. Herencsar, N., Koton, J., & Vrba, K. (2009). Single CCTA-Based Universal Biquadratic Filters Employing Minimum Components. *International Journal*

of Computer and Electrical Engineering, 1(3), 307. https://doi.org/10.7763/IJCEE.2009.V1.48

- 23. Horng, J.W., & Jhao, Z.Y. (2013). Voltage-mode universal biquadratic filter using single DVCC. *ISRN Electronics*, 2013. https://doi.org/10.1155/2013/125746

- 24. Ranjan, A., & Paul, S. K. (2011). Voltage mode universal biquad using CCCII. Active and Passive Electronic Components, 2011. https://doi.org/10.1155/2011/439052

- 25. Pushkar, K. L., Bhaskar, D. R., & Prasad, D. (2013). A new MISO-type voltage-mode universal biquad using single VD-DIBA. *ISRN Electronics*, 2013. https://doi.org/10.1155/2013/478213

- 26. Pathak, J. K., Singh, A. K., & Senani, R. (2013). New voltage mode universal filters using only two CD-BAs. *ISRN Electronics*, 2013. https://doi.org/10.1155/2013/987867

- 27. Chang, C. M., & Chen, H. P. (2003). Universal capacitor-grounded voltage-mode filter with three inputs and a single output. *International Journal of Electronics*, *90*(6), 401-406.

https://doi.org/10.1080/00207210310001612068

28. Chang, C. M., & Chen, H. P. (2005). Single FDCCIlbased tunable universal voltage-mode filter. *Circuits, Systems and Signal Processing, 24*(2), 221-227.

https://doi.org/10.1007/s00034-004-0422-7

29. Chiu, W. Y., & Horng, J. W. (2007). High-input and low-output impedance voltage-mode universal biquadratic filter using DDCCs. *IEEE Transactions on Circuits and Systems II: Express Briefs*, *54*(8), 649-652.

https://doi.org/10.1109/DELTA.2008.40

Yuce, E., & Tez, S. (2018). A novel voltage-mode universal filter composed of two terminal active devices. AEU-International Journal of Electronics and Communications, 86, 202-209. https://doi.org/10.1016/j.acup.2018.01.010

https://doi.org/10.1016/j.aeue.2018.01.010

- 31. Deliyannis, T., Sun, Y., & Fidler, J. K. (2019). Continuous-time active filter design. CRC press.

- 32. Chen, W. K., Chen, W. K., & Chen, W. K. (1995). The circuits and filters handbook. W. K. Chen (Ed.). USA: CRC Press.

Copyright © 2019 by the Authors. This is an open access article distributed under the Creative Com-

mons Attribution (CC BY) License (https://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Arrived: 24. 05. 2019 Accepted: 21. 10. 2019